【笔记】译码器

前言

译码器学习笔记

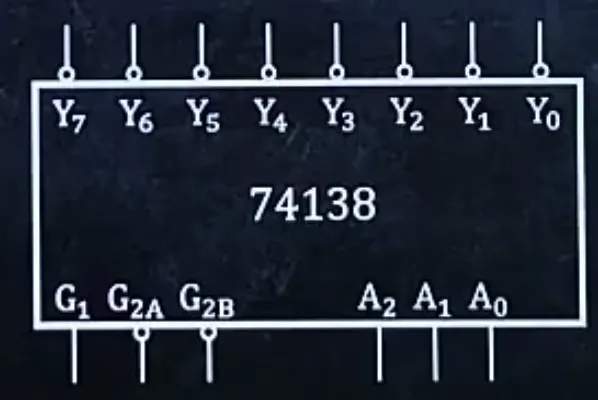

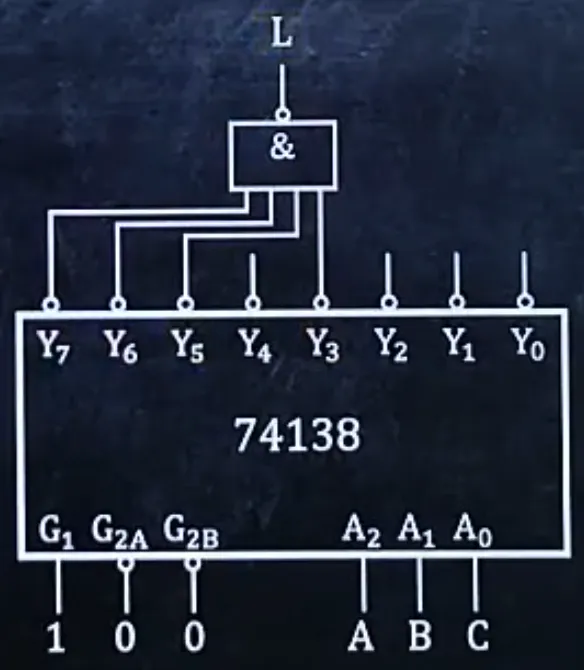

74138译码器的相关题型

题型1

- 给一个没有实现的74138译码器,实现逻辑函数表达式L

示例:给一个没有实现的74138译码器,实现逻辑函数表达式 L=AB+BC+AC

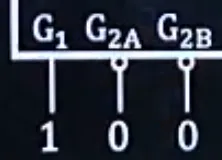

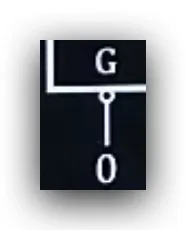

- 将译码器左下角G区添加标注

- 没有圈的标注为1

- 有圈的标注为0

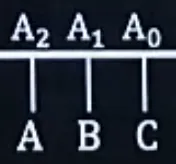

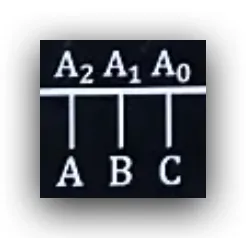

- 将译码器右下角A区添加标注

- 从左到右依次标注为A、B、C

- 将原逻辑函数转换成最小项形式

L=AB+AC+BC

L=ABC+ABC+ABC+ABC

L=m3+m5+m6+m7

- 将m转换成Y

L=Y3+Y5+Y6+Y7

- 化简(合并)

| 公式 |

|---|

| Y1+Y2=Y1·Y2 |

| Y1·Y2=Y1+Y2 |

L=Y3·Y5·Y6·Y7

- 根据得到的逻辑函数表达式L在译码器上接线

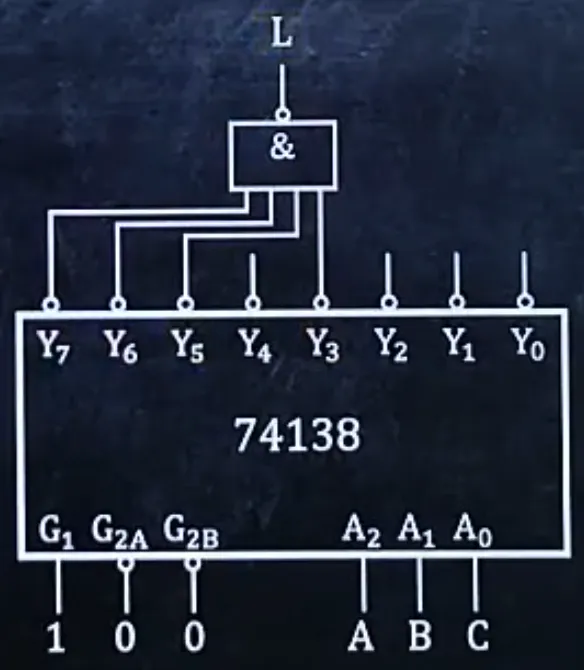

题型2

- 给一个已经实现的74138译码器,求逻辑函数表达式L

示例:给一个已经实现的74138译码器,求逻辑函数表达式L

- 根据译码器上的接线得到逻辑函数表达式L

L=Y3·Y5·Y6·Y7

- 将Y变成m

L=m3·m5·m6·m7

- 化简(拆分)

| 公式 |

|---|

| m1+m1=m1·m2 |

| m1·m1=m1+m2 |

L=m3+m5+m6+m7

L=m3+m5+m5+m7

- 将最小项转换成逻辑表达式L

3 5 6 7

011 101 110 111

L=ABC+ABC+ABC+ABC

- 用卡诺图法或公式法化简逻辑表达式L

L=AB+BC+AC

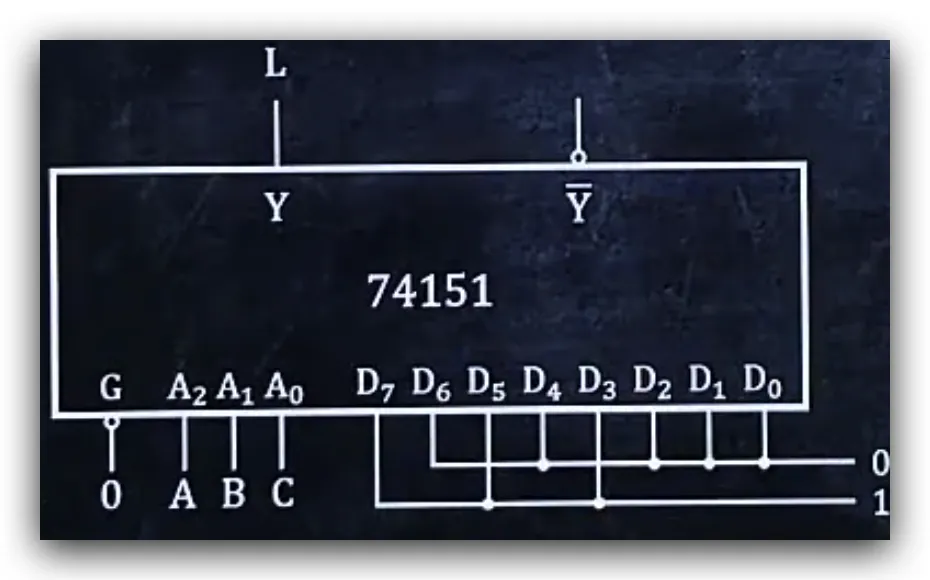

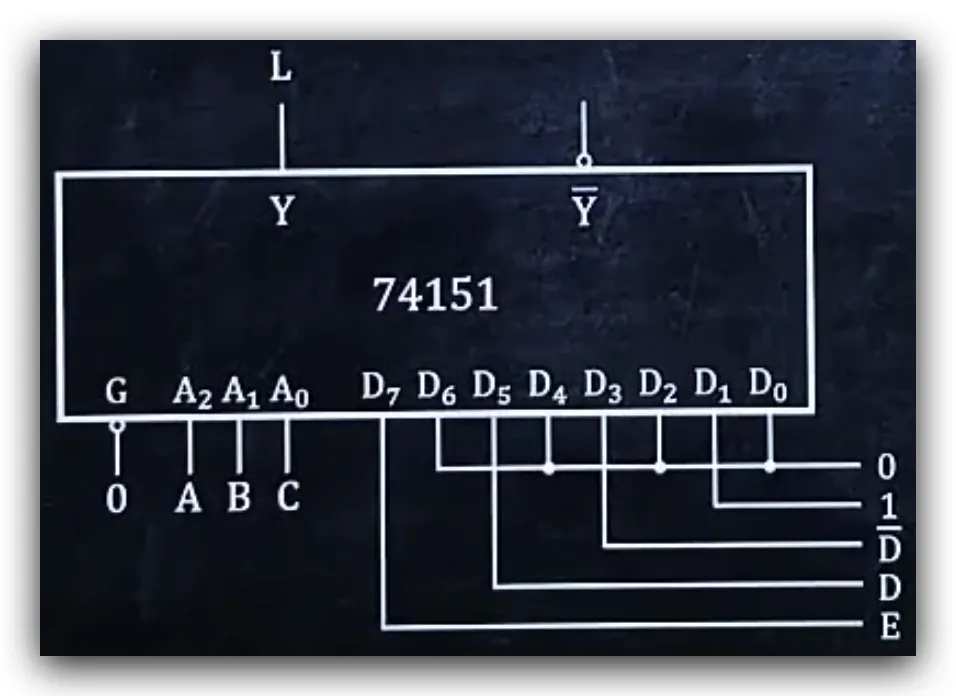

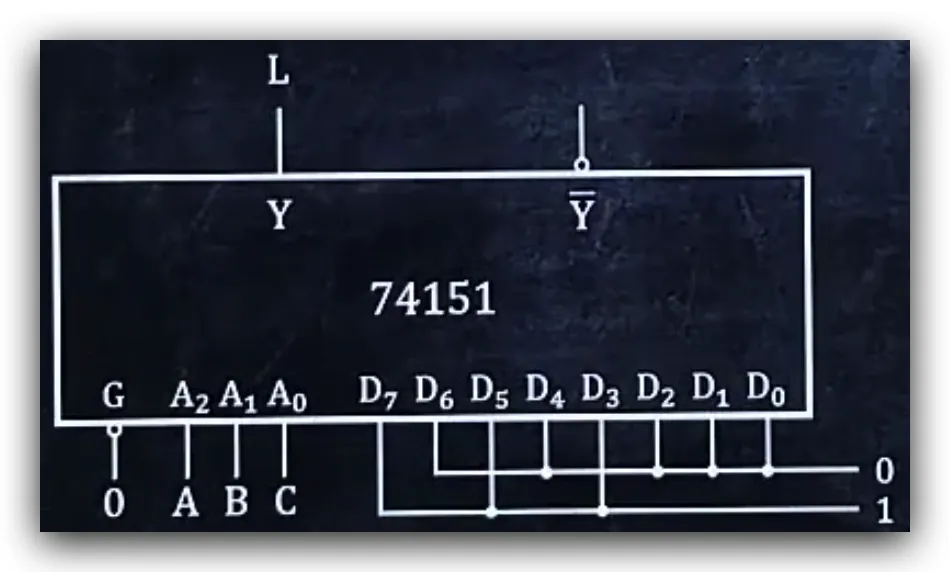

74151译码器的相关题型

题型1

- 给一个没有实现的74151译码器,实现3输入的逻辑函数表达式L

示例:给一个没有实现的74151译码器,实现逻辑函数表达式 L=ABC+ABC+ABC

- 将译码器左下角G区添加标注

- 没有圈的标注为1

- 有圈的标注为0

- 将译码器中下A区添加标注

- 从左到右依次标注为A、B、C

- 将原逻辑函数转换成最小项形式

L=ABC+ABC+ABC

L=m3+m5+m7

- 将m转换成D

L=D3+D5+D7

- 根据得到的逻辑函数表达式L在译码器上接线

- 将译码器右下角D区接线

- 存在就接1

- 不存在就接0

- 将译码器上Y区接线

- 如果L满足Y,就将L写在Y上

- 如果L满足Y,就将L写在Y上

题型2

- 给一个没有实现的74151译码器,实现多输入的逻辑函数表达式L

示例:给一个没有实现的74151译码器,实现多输入的逻辑函数表达式 L=ABC+ABCD+ABCD+ABCE

- 将译码器左下角G区添加标注

- 没有圈的标注为1

- 有圈的标注为0

- 将译码器中下A区添加标注

- 从左到右依次标注为A、B、C

- 无视除了ABC以外的字母,将原逻辑函数转换成最小项形式

L=m1+m5·D+m3·D+m7·E

- 将m转换成D

L=D1+D5·D+D3·D+D7·E

- 根据得到的逻辑函数表达式L在译码器上接线

- 将译码器右下角D区接线

- 先找到没有系数的D,将其接0

- 再将有系数的D,将其接其系数

- 将译码器上Y区接线

- 如果L满足Y,就将L写在Y上

- 如果L满足Y,就将L写在Y上

题型3

- 给一个没有实现的74151译码器,实现L=Σm格式的3输入的逻辑函数表达式L

示例:给一个没有实现的74151译码器,实现L=Σm格式的3输入的逻辑函数表达式 L=F(A,B,C)=Σm(3,5,7)

- 将译码器左下角G区添加标注

- 没有圈的标注为1

- 有圈的标注为0

- 将译码器中下A区添加标注

- 从左到右依次标注为A、B、C

- 根据Σm()转换成最小项形式

L=m3+m5+m7

- 将m转化成D

L=D3+D5+D7

- 根据得到的逻辑函数表达式L在译码器上接线

- 将译码器右下角D区接线

- 存在就接1

- 不存在就接0

- 将译码器上Y区接线

- 如果L满足Y,就将L写在Y上

- 如果L满足Y,就将L写在Y上

题型4

- 给一个没有实现的74151译码器,实现L=Σm格式的4输入的逻辑函数表达式L

示例:给一个没有实现的74151译码器,实现L=Σm格式的4输入的逻辑函数表达式 L=F(A,B,C,D)=Σm(0,3,5,8,13,15)

- 将译码器左下角G区添加标注

- 没有圈的标注为1

- 有圈的标注为0

- 将译码器中下A区添加标注

- 从左到右依次标注为A、B、C

- 根据Σm()转换成最小项形式

L=m0+m3+m5+m8+m13+m15

- 将最小项转化成最简逻辑函数表达式

L=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD

- 无视除了ABC以外的字母,将原逻辑函数转换成最小项形式,并提取公因数

L=m0·D+m1·D+m2·D+m4·D+m6·D+m7·D

L=D(m1+m2+m6+m7)+D(m0+m4)

- 将m转化成D

L=D(D1+D2+D6+D7)+D(D0+D4)

- 根据得到的逻辑函数表达式L在译码器上接线

- 将译码器右下角D区接线

- 先找到没有系数的D,将其接0

- 再将有系数的D,将其接其系数

- 将译码器上Y区接线

- 如果L满足Y,就将L写在Y上

- 如果L满足Y,就将L写在Y上

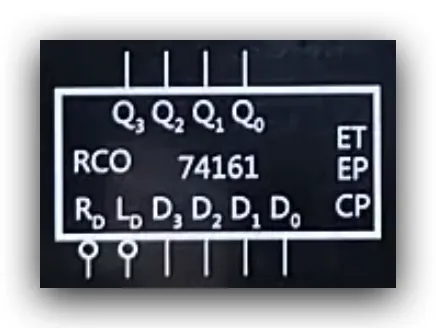

74161译码器的相关题型

题型1

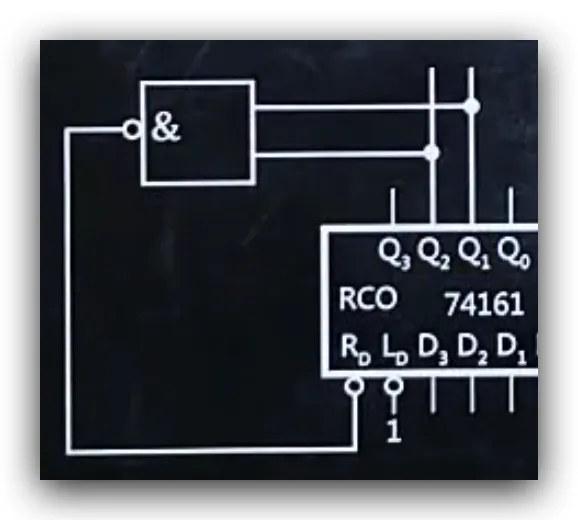

- 给一个没有实现的74161译码器,通过异步清零功能,设计n进制计算器

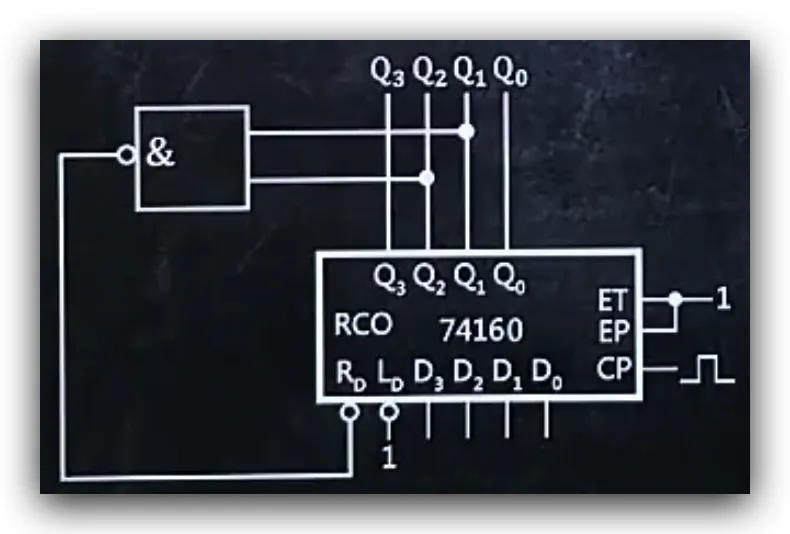

示例:给一个没有实现的74161译码器,通过异步清零功能,设计6进制计算器

- ET、EP连1

- CP连脉冲

- LD接口输入1

- 求出题目中进制数转换成4位二进制数的表示

6(D)=0110(B)

- 将Q3、Q2、Q1、Q0对应上一步骤得到的二进制数接线

- 在值为1的位上,先接非门,再接RD

- 如果有很多值为1的位,先一并将其接到与门,再接非门,最后接RD

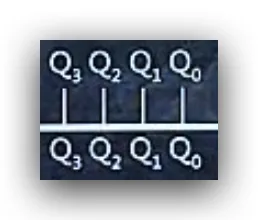

- 将Q3、Q2、Q1、Q0向上接对应的符号

题型2

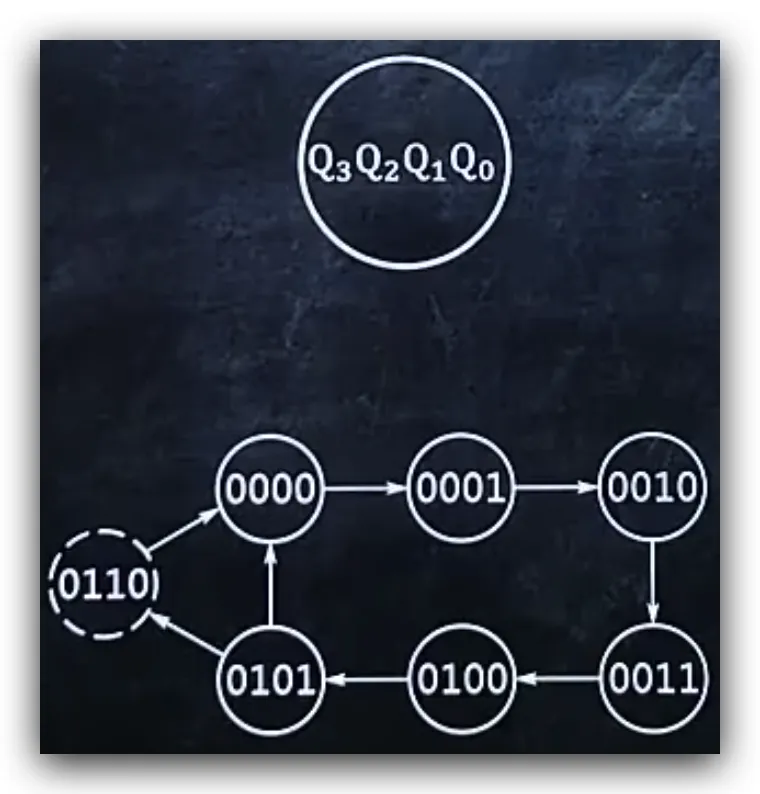

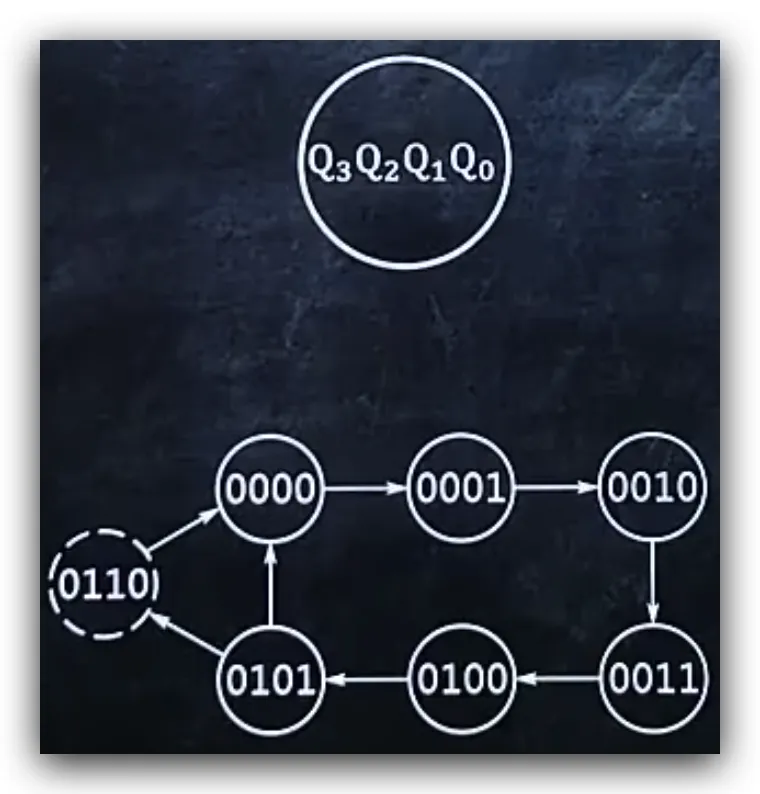

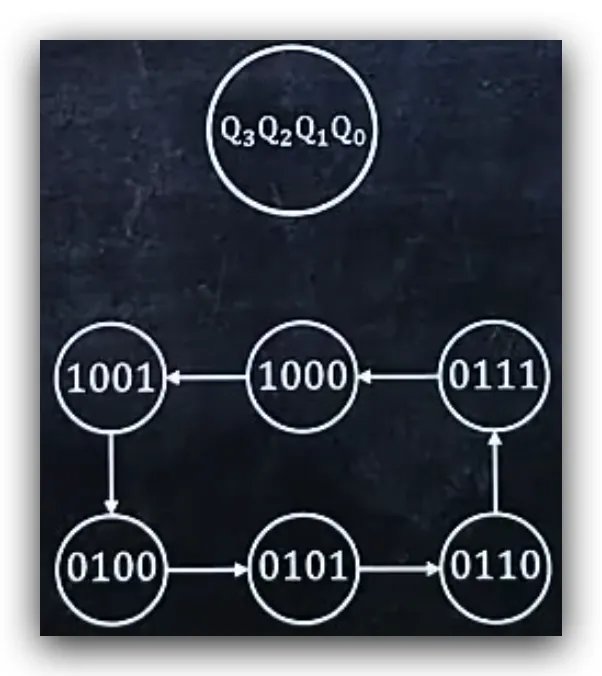

- 在上一题的基础上,画出状态图

示例:给一个没有实现的74161译码器,通过异步清零功能,设计6进制计算器,并画出状态图

写出0到n-1的4位二进制数

0(D)=0000(B)

1(D)=0001(B)

2(D)=0010(B)

3(D)=0011(B)

4(D)=0100(B)

5(D)=0101(B)

- 画图

- 画出Q3Q2Q1Q0,并用实线圆圈圈起来

- 画出所有0到n-1的4位二进制数,并用实线圆圈圈起来

- 根据从小到大的顺序画出箭头,最后n-1指向0

- 画出n的4位二进制数,并用虚线圆圈圈起来

- 画出箭头,n-1指向n,n指向0

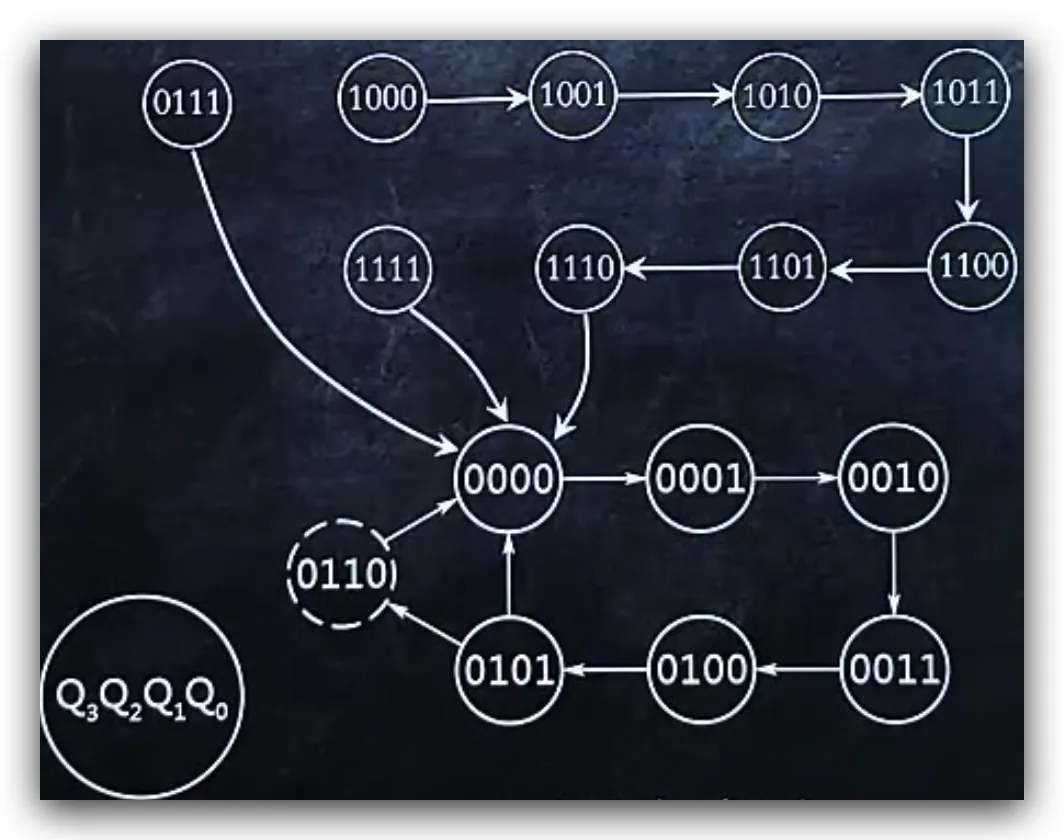

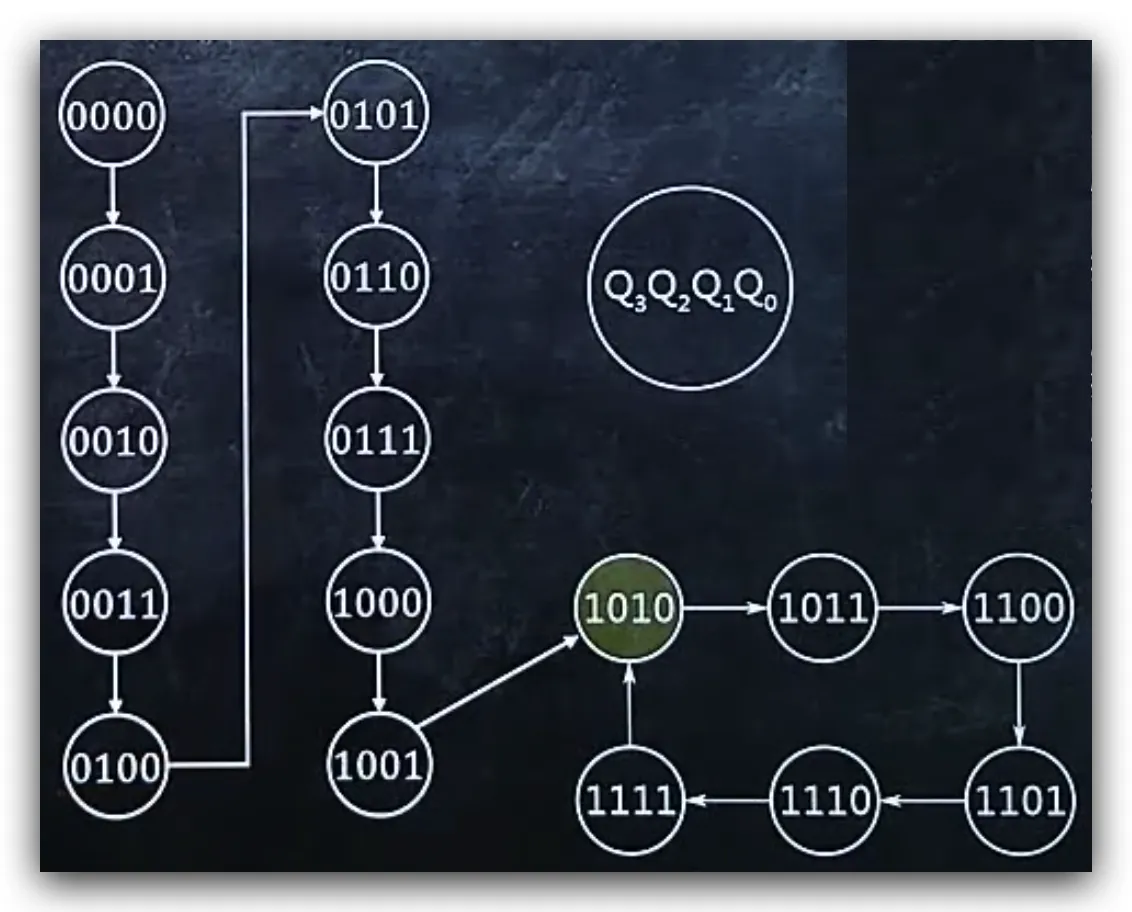

题型3

- 在上一题的基础上,检查自启动

示例:给一个没有实现的74161译码器,通过异步清零功能,设计6进制计算器,并画出状态图,检查能否自启动

7(D)=0111(B)

8(D)=1000(B)

9(D)=1001(B)

10(D)=1010(B)

11(D)=1011(B)

12(D)=1100(B)

13(D)=1101(B)

14(D)=1110(B)

15(D)=1111(B)

- 画图

- 画出所有n+1到15的4位二进制数,并用实现圆圈圈起来

- 找出n的4位二进制数哪那几个位上是1,将对应位置是1的二进制数全部画箭头指向n

- 将剩下的数根据从小到大的顺序画出箭头

- 最后回答

(一般异步清零题目很少有不能自启动的)

答:可以自启动

题型4

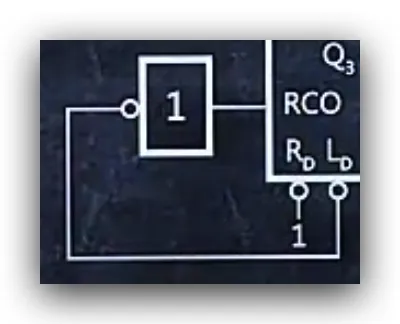

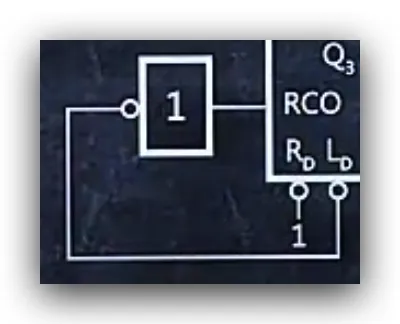

- 给一个没有实现的74161译码器,通过同步置数功能,设计n进制计算器

示例:给一个没有实现的74161译码器,通过同步置数功能,设计6进制计算器

- ET、EP连1

- CP连脉冲

- RD接口输入1

- 从4位二进制数1111开始递减n次,每次减1,并将递减第n次的4位二进制数,根据对应位置,在D3、D2、D1、D0上接对应数字

1111

1110

1101

1100

1011

1010

- 将RCO上连接非门,再连接LD

- 将Q3、Q2、Q1、Q0向上接对应的符号

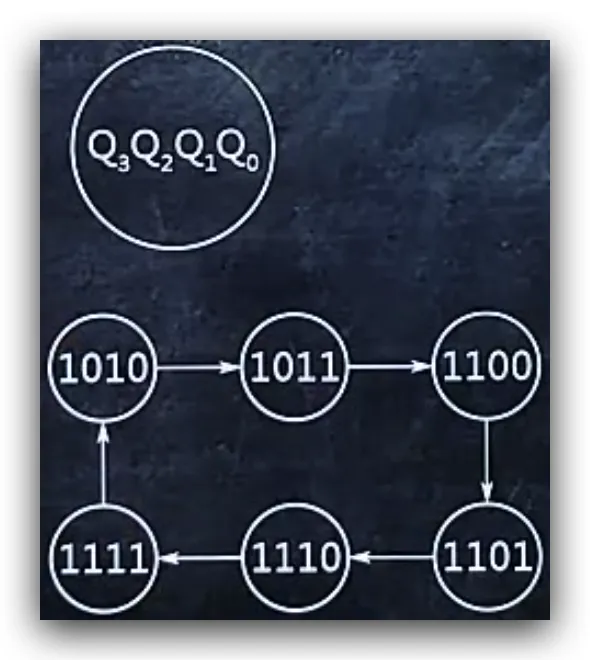

题型5

- 在上一题的基础上,画出状态图

示例:给一个没有实现的74161译码器,通过同步置数功能,设计6进制计算器,并画出状态图

从4位二进制数1111开始递减n次,每次减1

1111

1110

1101

1100

1011

1010

- 画图

- 画出Q3Q2Q1Q0,并用实线圆圈圈起来

- 画出所有从4位二进制数1111开始递减n次的4位二进制数,并用实线圆圈圈起来

- 根据从小到大的顺序画出箭头,最后1111指向第六次递减的4位二进制数

题型6

- 在上一题的基础上,检查自启动

示例:给一个没有实现的74161译码器,通过同步置数功能,设计6进制计算器,并画出状态图,检查能否自启动

0(D)=0000(B)

1(D)=0001(B)

2(D)=0010(B)

3(D)=0011(B)

4(D)=0100(B)

5(D)=0101(B)

6(D)=0110(B)

7(D)=0111(B)

8(D)=1000(B)

9(D)=1001(B)

- 画图

- 画出所有0到15-n的4位二进制数,并用实现圆圈圈起来

- 根据从小到大的顺序画出箭头,最大的数指向16-n

- 最后回答

(一般同步置数题目很少有不能自启动的)

答:可以自启动

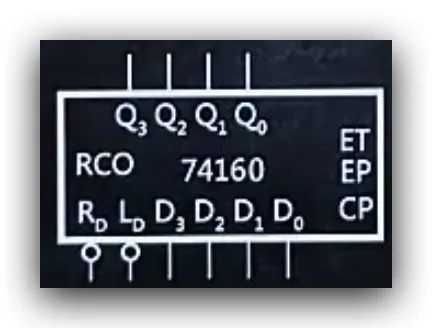

74160译码器的相关题型

- 74160的外部构造与74161完全相同

题型1

- 给一个没有实现的74160译码器,通过异步清零功能,设计n进制计算器

示例:给一个没有实现的74160译码器,通过异步清零功能,设计6进制计算器

- 完全按照74161的做法

题型2

- 在上一题的基础上,画出状态图

示例:给一个没有实现的74160译码器,通过异步清零功能,设计6进制计算器,并画出状态图

- 完全按照74161的做法

题型3

- 给一个没有实现的74160译码器,通过同步置数功能,设计n进制计算器

示例:给一个没有实现的74160译码器,通过同步置数功能,设计6进制计算器

- ET、EP连1

- CP连脉冲

- RD接口输入1

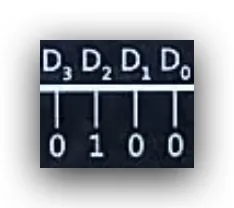

- 从4位二进制数1001开始递减n次,每次减1,并将递减第n次的4位二进制数,根据对应位置,在D3、D2、D1、D0上接对应数字

1001

1000

0111

0110

0101

0100

- 将RCO上连接非门,再连接LD

- 将Q3、Q2、Q1、Q0向上接对应的符号

题型4

- 在上一题的基础上,画出状态图

示例:给一个没有实现的74160译码器,通过同步置数功能,设计6进制计算器,并画出状态图

从4位二进制数1001开始递减n次,每次减1

1001

1000

0111

0110

0101

0100

- 画图

- 画出Q3Q2Q1Q0,并用实线圆圈圈起来

- 画出所有从4位二进制数1001开始递减n次的4位二进制数,并用实线圆圈圈起来

- 根据从小到大的顺序画出箭头,最后1001指向第六次递减的4位二进制数

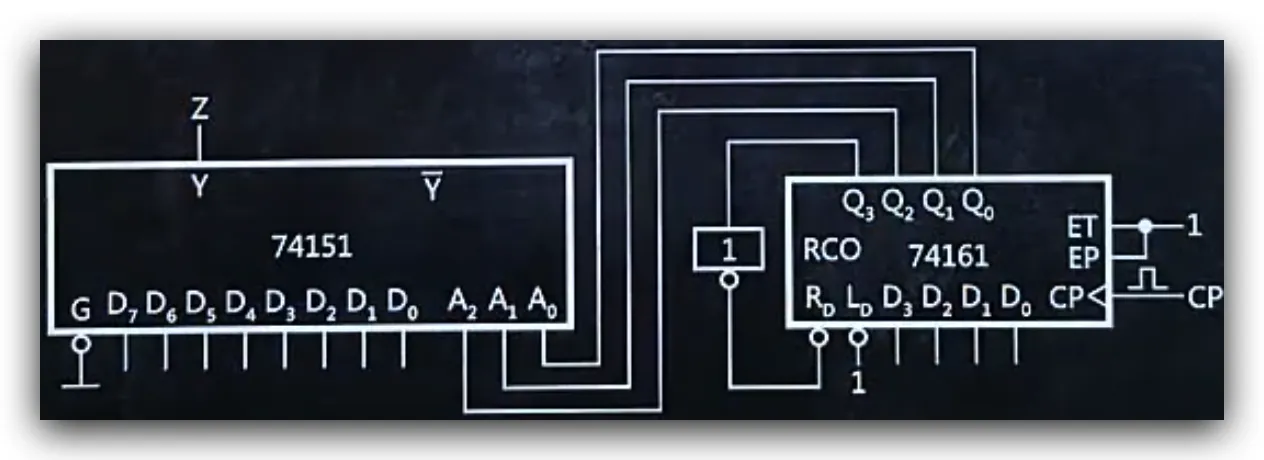

74161译码器和74151译码器组合题型

题型1

- 使用74161译码器和74151译码器设计序列发生器

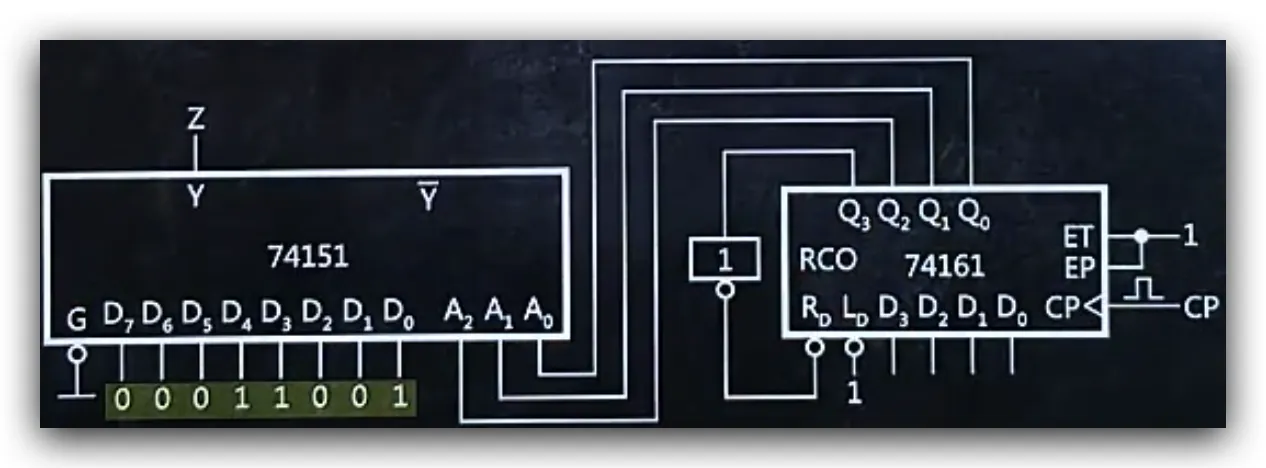

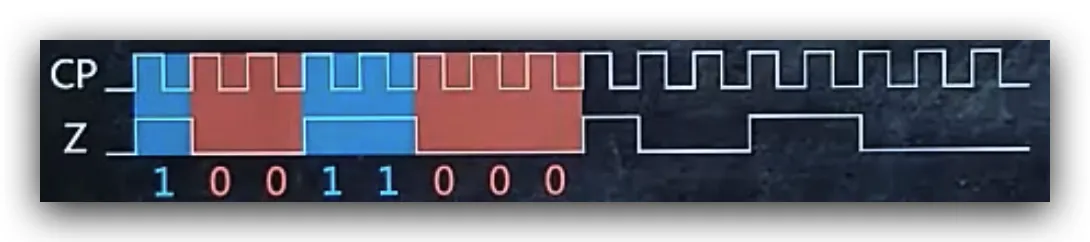

示例:试用计数器74161和数据选择器74151设计一个如下所示的序列发生器

- 根据图像找出循环的8位数

- 将CP线一高一低作为一组,每组对比Z线的高位还是低位

- 如果是高位,则为1

- 如果是低位,则为0

10011000

- 画出74161译码器和74151译码器组合

- 从D0开始,依次向D7写刚刚得到的8位数